# Lecture Notes for Course #236357 Distributed Algorithms

(Spring 1993)

Hagit Attiya

Department of Computer Science The Technion Haifa 32000, ISRAEL

January 30, 1994

# Preface

These lecture notes describe a course on distributed algorithms I taught in the department of computer science at the Technion during Spring, 1993. The course consisted of thirteen 1.5 hour lectures.

My goal in the course was not to provide comprehensive coverage of the area of distributed systems, and not even of the (more restricted) area of theory of distributed algorithms. Rather I wanted to present what I think are the rudiments of this area: the fundamental models, the canonical problems, and the basic methods. In many cases, I decided to present results that are not optimal when I thought they could shed light on the inherent features of some model, problem, or technique. In most of these cases, I mention the better results in the bibliographic notes at the end of the appropriate chapter.

The students have scribed the lectures based on my own notes and the original papers. Almost in all cases, they have filled in details and improved the rigor of the presentation. In several cases, they have fixed bugs and suggested simpler ways to present the material. Based on their scribed notes, I have prepared this manuscript. I have tried to unify notation and terminology and to point out similarities and relationships in the material.

I would like to remark that these notes are in a very preliminary form and miss many things. In particular, the credits in the bibliographic notes are not always complete or precise. If you have any comments about these notes, please send electronic mail to hagit@cs.technion.ac.il.

I would like to thank the students who took this course in Spring, 1993 for their excellent work. The following students scribed lectures (in the order of lectures): Ophir Rachman, Eyal Dagan and Eli Stein, Galia Givaty and Amnon Horowitz, Gitit Sadeh and Liat Harari, Ido Barnea and Avi Telyas, Liviu Asnash and Boaz Shaham, Guy Bashkansky and Boris Farizon, Simona Holstein and Osnat Arad, Irina Notkin and Alex Dubrovski, Martha Ben-Michael and Rivki Matosevich. Roy Petrushka and Ori Dgani.

Ophir Rachman, the teaching assistant in the course, has gone through several versions

of the notes scribed by the students. His perfectionism and diligence made them into a very good starting point. Thanks also to Ran Canetti for his guest lecture on randomized consensus algorithms.

I have consulted with Jennifer Welch several times during the preparation of the course about choice of topics and content. Yehuda Afek, Amir Ben-Dor, Marios Mavronicolas, Hadas Shachnai, and Jennifer Welch read early versions of these notes and the comments they provided were most helpful in improving the presentation in several places. All the mistakes that remain are entirely my own.

My work is supported by the US-Israel Binational Science Foundation, Technion V.P.R.—Argentinian Research Fund, and the fund for the promotion of research in the Technion. Part of my work on these notes was carried out during summer, 1993, when I visited AT&T Bell Laboratories in Murray Hill, New Jersey.

Hagit Attiya January, 1994

# Contents

| Ι | Me                         | ssage Passing Systems                                                                                  | 7  |  |  |

|---|----------------------------|--------------------------------------------------------------------------------------------------------|----|--|--|

| 1 | Intro                      |                                                                                                        |    |  |  |

|   | 1.1                        | Definition of the Computation Model                                                                    | 10 |  |  |

|   | 1.2                        | Overview of this Part $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 12 |  |  |

|   | 1.3                        | Bibliographic Notes                                                                                    | 12 |  |  |

| 2 | 2 Leader Election in Rings |                                                                                                        |    |  |  |

|   | 2.1                        | The Problem                                                                                            | 13 |  |  |

|   | 2.2                        | Anonymous Rings                                                                                        | 14 |  |  |

|   | 2.3                        | Asynchronous Rings                                                                                     | 15 |  |  |

|   |                            | 2.3.1 An $O(n^2)$ Algorithm                                                                            | 15 |  |  |

|   |                            | 2.3.2 An $O(n \log n)$ Algorithm                                                                       | 16 |  |  |

|   |                            | 2.3.3 An $\Omega(n \log n)$ Lower Bound                                                                | 18 |  |  |

|   | 2.4                        | Synchronous Rings                                                                                      | 23 |  |  |

|   |                            | 2.4.1 An $O(n)$ Upper Bound                                                                            | 24 |  |  |

|   |                            | 2.4.2 An $\Omega(n \log n)$ Lower Bound for Restricted Algorithms                                      | 28 |  |  |

|   | 2.5                        | Bibliographic Notes                                                                                    | 37 |  |  |

|   | 2.6                        | Exercises                                                                                              | 37 |  |  |

| 3 | Lead                    | ler Election in Complete Networks                                                                     | 39 |  |  |  |

|---|-------------------------|-------------------------------------------------------------------------------------------------------|----|--|--|--|

|   | 3.1                     | An $O(n \log n)$ Upper Bound for Asynchronous Networks                                                | 40 |  |  |  |

|   |                         | 3.1.1 A Detailed Description of the Algorithm                                                         | 40 |  |  |  |

|   |                         | 3.1.2 Correctness and Complexity                                                                      | 40 |  |  |  |

|   | 3.2                     | An $\Omega(n \log n)$ Lower Bound for Synchronous Networks                                            | 43 |  |  |  |

|   | 3.3                     | Bibliographic Notes                                                                                   | 47 |  |  |  |

| 4 | MST in General Networks |                                                                                                       |    |  |  |  |

|   | 4.1                     | The Minimum Spanning Tree Problem                                                                     | 49 |  |  |  |

|   | 4.2                     | Preliminaries                                                                                         | 49 |  |  |  |

|   | 4.3                     | The Distributed MST Algorithm                                                                         | 50 |  |  |  |

|   |                         | 4.3.1 Informal Description of the Algorithm                                                           | 51 |  |  |  |

|   |                         | 4.3.2 Detailed Description of the Algorithm                                                           | 52 |  |  |  |

|   | 4.4                     | Proof of Correctness (Sketch) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 56 |  |  |  |

|   | 4.5                     | Message Complexity                                                                                    | 59 |  |  |  |

|   | 4.6                     | Bibliographic Notes                                                                                   | 60 |  |  |  |

|   | 4.7                     | Exercises                                                                                             | 60 |  |  |  |

| 5 | $\mathbf{Syn}$          | chronizers                                                                                            | 62 |  |  |  |

|   | 5.1                     | Motivating Example: Constructing a Breath-First Tree                                                  | 63 |  |  |  |

|   | 5.2                     | Notation                                                                                              | 64 |  |  |  |

|   | 5.3                     | Description of Synchronizers                                                                          | 65 |  |  |  |

|   |                         | 5.3.1 Synchronizer $\alpha$                                                                           | 65 |  |  |  |

|   |                         | 5.3.2 Synchronizer $\beta$                                                                            | 66 |  |  |  |

|   |                         | 5.3.3 Synchronizer $\gamma$                                                                           | 66 |  |  |  |

|   | 5.4                     | The Partition Algorithm                                                                               | 68 |  |  |  |

|   |                         | 5.4.1 Outline of the Algorithm                                                                        | 69 |  |  |  |

|   |                         | 5.4.2 The Cluster Creation Procedure                                                                  | 69 |  |  |  |

|                |                                            | 5.4.3                                       | The Search for Leader Procedure                                                   | 71   |  |  |  |

|----------------|--------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|------|--|--|--|

|                |                                            | 5.4.4                                       | The Preferred Edges Selection Procedure                                           | 72   |  |  |  |

|                |                                            | 5.4.5                                       | Complexity of the Partition Algorithm                                             | 73   |  |  |  |

| 5.5            |                                            | 5 Bibliographic Notes                       | graphic Notes                                                                     | . 74 |  |  |  |

|                | 5.6                                        | Exerc                                       | ises                                                                              | . 74 |  |  |  |

| 11             | [ Sł                                       | nared                                       | Memory Systems                                                                    | 77   |  |  |  |

| 6              | Intr                                       | oducti                                      | on                                                                                | 79   |  |  |  |

|                | 6.1                                        | Defini                                      | tion of the Computation Model                                                     | . 79 |  |  |  |

|                | 6.2                                        | Overv                                       | iew of this Part                                                                  | 81   |  |  |  |

| 7              | Mut                                        | Mutual Exclusion using Read/Write Registers |                                                                                   |      |  |  |  |

|                | 7.1                                        | The B                                       | akery Algorithm                                                                   | 83   |  |  |  |

|                | 7.2                                        | A Bou                                       | unded Mutual Exclusion Algorithm for Two Processors                               | 86   |  |  |  |

|                | 7.3                                        | A Bou                                       | unded Mutual Exclusion Algorithm for $n$ Processors $\ldots \ldots \ldots \ldots$ | 89   |  |  |  |

|                | 7.4                                        | Lower                                       | Bound on the Number of Read/Write Registers                                       | 92   |  |  |  |

|                | 7.5                                        | Biblio                                      | graphic Notes                                                                     | . 97 |  |  |  |

|                | 7.6                                        | Exerc                                       | ises                                                                              | 99   |  |  |  |

| 8              | Mutual Exclusion Using Powerful Primitives |                                             |                                                                                   |      |  |  |  |

|                | 8.1                                        | Binar                                       | y Test&Set Registers                                                              | 100  |  |  |  |

|                | 8.2                                        | Read-                                       | Modify-Write Registers                                                            | 102  |  |  |  |

|                | 8.3                                        | Lower                                       | Bound on the Number of Memory States                                              | 103  |  |  |  |

|                | 8.4                                        | Biblio                                      | graphic Notes                                                                     | 104  |  |  |  |

|                | 8.5                                        | Exerc                                       | ises                                                                              | 104  |  |  |  |

| IJ             | IF                                         | ault-T                                      | Colerance                                                                         | 105  |  |  |  |

| 9 Introduction |                                            |                                             |                                                                                   |      |  |  |  |

| 10Synchronous Systems I: Benign Failures            | 109 |

|-----------------------------------------------------|-----|

| 10.1 The Coordinated Attack Problem                 | 109 |

| 10.2 The Consensus Problem                          | 111 |

| 10.2.1 A Simple Algorithm                           | 112 |

| 10.2.2 Lower Bound on the Number of Rounds          | 113 |

| 10.3 Bibliographic Notes                            | 120 |

| 10.4 Exercises                                      | 120 |

| 11Synchronous Systems II: Byzantine Failures        | 122 |

| 11.1 The Ratio of Faulty Processors                 | 123 |

| 11.2 An Exponential Algorithm                       | 126 |

| 11.3 A Polynomial Algorithm                         | 129 |

| 11.3.1 The Authenticated Broadcast Primitive        | 129 |

| 11.3.2 Consensus Using Authenticated Broadcast      | 130 |

| 11.3.3 An Implementation of Authenticated Broadcast | 132 |

| 11.4 Bibliographic Notes                            | 134 |

| 11.5 Exercises                                      | 135 |

| 12Asynchronous Systems                              | 136 |

| 12.1 Impossibility of Deterministic Solutions       | 137 |

| 12.1.1 Shared Memory Model                          | 137 |

| 12.1.2 Message Passing Model                        | 143 |

| 12.2 Randomized Algorithms                          | 146 |

| 12.2.1 The Building Blocks                          | 147 |

| 12.2.2 The Algorithm                                | 148 |

| 12.2.3 Proof of Correctness                         | 148 |

| 12.2.4 Implementation of the Building Blocks        | 150 |

| 12.3 Bibliographic Notes                            | 154 |

| 12.4 Exercises                                      | 154 |

# Part I

# Message Passing Systems

# Chapter 1

# Introduction

In the first part of the course we focus on *message passing systems*, one of the most important models for distributed systems. A message passing system is described by a *communica-tion graph*, where the nodes of the graph represent the processors, and (undirected) edges represent two-way communication channels between processors. Each processor is an independent processing unit equipped with local memory, and is running a local program. The local programs contain internal operations, sending messages (on some edges), and waiting for messages (on some edges). An algorithm for the system is a collection of local programs for the different processors. An execution of the algorithm is the interleaved execution of the local programs (under some restrictions).

Several variants of message passing systems have been studied in the theory of distributed computing. These variants are distinguished according to the following features:

- The communication graph: The graph may be of some standard form, e.g., a ring, a clique, or the graph may be arbitrary.

- **Degree of synchrony:** The system can be *synchronous*, where the computation is performed in *rounds*. At the beginning of a round each processor sends messages, and waits to receive messages that were sent by its neighbors in this round. Upon receiving these messages, the processor performs some internal operations, and then decides what messages to send in the next round. In an *asynchronous* system, processors operate at arbitrary rates which might vary over time. In addition, messages incur an unbounded and unpredictable (but finite) delay. There are also intermediate models of partially synchronous systems, which will not be discussed here.

- **Degree of symmetry:** In an *anonymous* system, all the processors are completely identical, without individual names or id's. In other words, in an anonymous system, the

local programs of all the processors are identical. In a system with distinct id's, each processor has a distinct name, typically an integer number.

**Uniformity:** In a *uniform* system, a processor does not know the total number of processors in the system. Consequently, a processor runs exactly the same program regardless of the size of the system. On the other hand, in a non-uniform system, processors know the size of the system, and can therefore use it to run different programs according to the size of the system.

The above characteristics and a few others specify the exact model of a message passing system. As we shall see, in some cases, these characteristics have a great effect on the power of the system. We shall see problems that may be solved easily in one model, while in another model many resources are required to solve them. Moreover, we shall see problems that can be solved in one model, but not in another.

## **1.1** Definition of the Computation Model

Here we outline the basic elements of our formal model of message passing systems.

The computation in such systems proceeds through a sequence of configurations. In the initial configuration, processors are in an initial state, and all edges are empty. The execution of the algorithm consists of events; the possible events are a processor executing an internal operation, a message being sent on some edge, or a message delivered at its destination. Each event either changes the state of some processor, or changes the state of some edge, and thereby, changes the configuration of the system.

In more detail, an *algorithm* consists of *n* processors  $p_1, \ldots, p_n$ . Each processor  $p_i$  is modeled as a (possibly infinite) state machine with state set  $Q_i$ . The state set  $Q_i$  contains a distinguished *initial state*,  $q_{0,i}$ . We assume the state of processor  $p_i$  contains a special component,  $buff_i$ , in which incoming messages are buffered.

A configuration is a vector  $C = (q_1, \ldots, q_n)$  where  $q_i$  is the local state of  $p_i$ . The initial configuration is the vector  $(q_{0,1}, \ldots, q_{0,n})$ . Processors communicate by sending messages (taken from some alphabet  $\mathcal{M}$ ) to each other. A send action send(i, j, m) represents the sending of message m from  $p_i$  to  $p_j$ . For any  $i, 1 \leq i \leq n$ , let  $\mathcal{S}_i$  denote the set of all send actions send(i, j, m) for all  $m \in \mathcal{M}$  and all  $j, 1 \leq j \leq n$ .

We model a computation of the algorithm as a sequence of configurations alternating with *events*. Each event is either a *computation event*, representing a computation step of a single processor or a *delivery event*, representing the delivery of a message to a processor. A computation event is specified by comp(i, S) where *i* is the index of the processor taking the step and *S* is a finite subset of  $S_i$ . In the computation step associated with event comp(i, S), the processor  $p_i$ , based on its local state, performs the *send* actions in *S* and possibly changes its local state. Each delivery event has the form del(i, j, m) for some  $m \in \mathcal{M}$ . In the delivery step associated with event del(i, j, m) the message *m* from  $p_i$  is added to  $buff_i$ .

An *execution segment*  $\alpha$  of an algorithm is a (finite or infinite) sequence of the following form:

$$C_0, \phi_0, C_1, \phi_1, C_2, \phi_2 \dots$$

where  $C_k$  are configurations, and  $\phi_k$  are events. Furthermore, the application of  $\phi_k$  to  $C_k$  results in  $C_{k+1}$ , in the natural way. That is, if  $\phi_k$  is a local computation event of processor  $p_i$  then the state of  $p_i$  in  $C_{k+1}$  and its message send events are the result of applying  $p_i$ 's transition function to the state of  $p_i$  in  $C_k$ ; if  $\phi_k$  is a message sending or delivery event then the state of appropriate edge is changed accordingly. (These are the only changes.)

We adopt the convention that a finite execution segment ends with a configuration. If  $\alpha$  is a finite execution segment, then  $C_{end}(\alpha)$  denotes the last configuration in  $\alpha$ .

An execution is an execution segment  $C_0, \phi_0, C_1, \phi_1, C_2, \phi_2 \dots$ , where  $C_0$  is the initial configuration, With each execution we associate a *schedule* which is the sequence of events in the execution, that is  $\phi_0, \phi_1, \phi_2, \dots$  Notice that if the local programs are deterministic, then the execution is uniquely determined by the initial configuration and the schedule.

In most cases, we would like to put further requirements on executions, e.g., that all messages sent are eventually delivered. This is captured by the notion of *admissibility*.

In the asynchronous model, an execution is *admissible* if each processor has an infinite number of computation events, and there is a one-to-one mapping from the send actions to later delivery events. (This guarantees that every message sent is delivered at some later point in the execution.) We sometimes assume that processor  $p_i$  has a computation event immediately after each delivery event of the form del(j, i, m). In this case, we merge the message delivery event and the computation event and refer to the computation taken by the processor upon receiving the message.

In the synchronous model processors execute in lock-step. An execution is *admissible* if, in addition to the asynchronous admissibility constraints mentioned earlier, the computation events appear in *rounds*. We assume that each processor has exactly one computation event in each round and that computation events of round r appear after all computation events of round r - 1. Furthermore, we assume all messages sent in round r are delivered before the computation events of round r + 1.

## 1.2 Overview of this Part

In the next chapters we discuss several basic algorithms and lower bounds, mostly on message complexity, for computation in message-passing systems. We start with the problem of electing a leader in ring-shaped networks, which represents a host of symmetry breaking problems. We present upper and lower bounds for the number of messages required to elect a leader, for synchronous and asynchronous models. The next chapter studies leader election in complete networks. We then turn to message-passing systems with arbitrary communication network. We discuss the problem of constructing a minimum spanning tree in a general network. We then show how to construct several synchronizers in a general network. A synchronizer allows one to run algorithms designed for synchronous systems on asynchronous systems.

Throughout this part, we assume that processors and communication links are reliable and function correctly. We will return to issues of fault-tolerance in a later part of these lecture notes.

## **1.3 Bibliographic Notes**

Our formal model of a distributed system is based on the I/O Automaton model of Lynch and Tuttle [45], as simplified for our purposes. The main difference is that our model does not incorporate composition of automata, and does not address general issues of fairness in the composed system. Our model borrows key components from papers such as [31, 32].

# Chapter 2

# Leader Election in Rings

We start our discussion of message passing systems by studying message passing systems in which the communication graph is a ring. Rings are a very convenient structure for message passing systems and correspond to physical communication systems, e.g., token rings. We investigate the *leader election* problem, in which the processors must "choose" one of the processors to be the leader. The existence of a leader can simplify coordination among processors and is helpful in achieving fault-tolerance and saving resources. Furthermore, the leader election problem represents a general class of symmetry breaking problems; the techniques we develop for it will be useful later for other problems.

# 2.1 The Problem

The leader election problem has several variants, and we define the most general one below. We assume the processors have no input values, and the last operation in each local program of a processor must be a write to a Boolean variable, representing whether the processor is the leader or not. In order for an algorithm to solve the leader election problem it is required that when all the local programs terminate, exactly one processor sets the variable to *true*; this processor is the *leader* elected by the algorithm. All other processors set the variable to *false*.

Other variants of the problem exist. For example, in a system with distinct id's, one may require that the leader must be the processor with the maximal id. Also one may require that all processors will know the id of the elected leader.

We assume that the ring is *oriented*, that is, processors distinguish between the links to their left and their right neighbors. Furthermore, if  $p_i$  is  $p_j$ 's left neighbor then  $p_j$  is  $p_i$ 's right neighbor. (See the bibliographic notes.)

# 2.2 Anonymous Rings

We show that there is no deterministic leader election algorithm for anonymous rings. For generality and simplicity, we prove the result for synchronous rings; this immediately implies the same result for asynchronous rings.

In any algorithm for an anonymous ring, all processors are identical and execute the same program. Recall that in a synchronous system, an algorithm proceeds in rounds, where in each round a processor receives messages that were sent to it in that round, performs a local computation and then sends messages. Note that the local programs in such an algorithm have the following structure:

In the first round, a processor sends some initial set of messages. In the second round, the processor receives the messages sent in the first round, and it executes some conditional statement that decides what messages should be sent in the second round. This continues until, at some round, after receiving messages the processor decides to terminate the program. At this point the processor writes to the Boolean output variable either *true* ("I am the leader") or *false* ("I am not the leader").

Intuitively, the idea is that in an anonymous ring, the symmetry between the processors can always be maintained, so without some initial asymmetry (as provided by unique id's), it cannot be broken. Specifically, all processors in the anonymous ring start in the same state. Since they are identical, in every round each of them sends exactly the same messages; thus, they all receive the same messages in each round. Consequently, if one of the processors terminates its program by winning, then so do all processors. Hence, it is impossible to have an algorithm that elects a single leader in the ring.

To formalize this intuition, consider an anonymous ring of size n > 1, and assume, by way of contradiction, that there exists a deterministic algorithm, A, for electing a leader in this ring. (We assume the algorithm is non-uniform, that is, n is known to the processors.)

**Lemma 2.2.1** Let A be an anonymous non-uniform algorithm. For every round k, the states of all the processors at the end of round k are the same.

**Proof:** The proof is by induction on k. The base case, k = 1, is straightforward since the processors start the same program in the same initial state.

For the induction step, assume the lemma holds for round k - 1. Since the processors are in the same state in round k - 1, they all send the same message  $m_r$  to the right, and the same message  $m_\ell$  to the left. In round k, every processor receives the message  $m_\ell$  on its right edge, and the message  $m_r$  on its left edge. Thus, all the processors receive exactly the same messages in round k, and since they execute the same program, they are in the same state at the end of round k + 1.

The above lemma implies that if at the end of some round some processor announces itself as a leader, so do all other processors. This contradicts the assumption that A is a leader election algorithm and proves:

**Theorem 2.2.2** There is no non-uniform algorithm for leader election in anonymous rings.

### 2.3 Asynchronous Rings

In this section we show upper and lower bounds for the leader election problem in asynchronous rings. Following Theorem 2.2.2, we assume that processors have distinct id's.

We start with a very simple leader election algorithm for asynchronous rings that requires  $O(n^2)$  messages. This algorithm motivates a more efficient algorithm that requires  $O(n \log n)$  messages. We show that this algorithm has optimal message complexity by proving a lower bound of  $\Omega(n \log n)$  on the number of messages required for electing a leader.

### **2.3.1** An $O(n^2)$ Algorithm

In this algorithm, each processor sends a message with its id to its left neighbor, and then waits for messages from its right neighbor. When it receives such a message, it checks the id in this message. If the id is greater than its own id, it forwards the message to the left; otherwise, it "swallows" the message and does not forward it. If a processor receives a message with its own id, it declares itself a leader by sending a termination message to its left neighbor, and exiting the algorithm as a leader. A processor that receives a termination message forwards it to the left, and exits as a non-leader. Notice that the algorithm does not use the size of the ring.

Note that only the message of the processor with the maximal id is never swallowed. Therefore, only the processor with the maximal id receives a message with its own id and will declare itself as a leader. All the other processors receive termination messages and are not chosen as leaders. This implies the correctness of the algorithm.

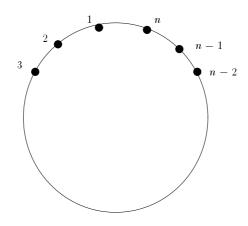

Figure 2.1: Label assignment.

Clearly, the algorithm never sends more than  $O(n^2)$  messages. Moreover, there is an execution in which the algorithm sends  $O(n^2)$  messages: Consider the ring where the id's of the processors are  $1, \ldots, n$ , and they are ordered such that i is the left neighbor of i + 1 (modulo n); see Figure 2.1. In this configuration, the message of processor i is forwarded exactly i times. Thus, the total number of messages (not including the n termination messages) is  $\sum_{i=0}^{n-1} i = O(n^2)$ .

### **2.3.2** An $O(n \log n)$ Algorithm

The more efficient algorithm is based on the same idea as the algorithm we have just seen. Again, a processor sends its id around the ring, and the algorithm guarantees that only the message of the processor with the maximal id traverses the whole ring and returns. However, the algorithm employs a more clever method for forwarding id's, thus reducing the worst case number of messages from  $O(n^2)$  to  $O(n \log n)$ .

To describe the algorithm, we first define the *k*-neighborhood of a processor  $p_i$  in the ring to be the set of processors that are at distance at most k from  $p_i$  in the ring (either to the left or to the right). Note that the *k*-neighborhood of a processor includes exactly 2k + 1 processors. The algorithm operates in phases. In the  $\ell$ th phase a processor tries to be the temporary leader of its  $2^{\ell}$ -neighborhood. Only processors that are temporary leaders in the  $\ell$ th phase continue to the  $(\ell + 1)$ th phase. Thus, fewer processors proceed to higher phases, until at the end, only one processor is elected as the leader of the whole ring.

In more detail, in phase 0, each processor sends a message containing its id to its 1neighborhood, i.e., to each of its two neighbors. If the id of the neighbor receiving the message is greater than the one in the message, it swallows the message; otherwise, it returns the message. If the messages of a processor return from both its neighbors, then the processor is the temporary leader of its 1-neighborhood, and continues to phase 1.

In general, in phase  $\ell$ , a processor  $p_i$  that was a temporary leader in phase  $\ell - 1$  sends messages with its id to its  $2^{\ell}$ -neighborhood (one in each direction). Each such message traverses  $2^{\ell}$  processors one by one. A message is swallowed by a processor if it contains an id that is smaller than its own id. If the message arrives at the last processor in the neighborhood without being swallowed, then that last processor returns the message to  $p_i$ . If  $p_i$ 's messages return from both directions, it is the temporary leader of its  $2^{\ell}$ -neighborhood, and it continues to phase  $\ell + 1$ . A processor that receives on its left edge a message that it sent on its right edge (or vice versa), terminates the algorithm as the leader, and sends a termination message around the ring.

Notice that in order to implement the algorithm the last processor in a  $2^{\ell}$ -neighborhood must return the message rather than forward it. Thus, we have three fields in each message: The id, the phase number  $\ell$ , and a hop counter. The hop counter is initialized to 0, and is incremented whenever a processor forwards the message. If a processor receives a phase  $\ell$  message with a hop counter  $2^{\ell}$ , then it is the last processor in the  $2^{\ell}$ -neighborhood.

The correctness of the algorithm follows in the same manner as in the simple algorithm, since they have the same swallowing rules. It is clear that the messages of the processor with the maximal id are never swallowed; therefore, this processor will terminate the algorithm as a leader. On the other hand, it is also clear that no other message can traverse the whole ring without being swallowed. Therefore, the processor with the maximal id is the only leader elected by the algorithm.

To analyze the worst case number of messages that is sent during the algorithm, we first prove:

**Lemma 2.3.1** For any l > 1, the number of processors that are temporary leaders in phase l is less than or equal to  $\frac{n}{2^{l-1}}$ .

**Proof:** Note that if processor  $p_i$  continues to phase  $\ell$ , then it is guaranteed that all the processors in  $p_i$ 's  $2^{\ell-1}$ -neighborhood have id's smaller then  $p_i$ . Otherwise, one of them would have swallowed  $p_i$ 's message in phase  $\ell - 1$ . Therefore, no processor in  $p_i$ 's  $2^{\ell-1}$ -neighborhood is a temporary leader in phase  $\ell - 1$ . Hence, between any two consecutive processors that are temporary leaders in phase  $\ell$  there are at least  $2^{\ell-1}$  processors that are

not. Thus, the total number of processors that are temporary leaders in phase  $\ell$  is at most  $\frac{n}{2^{\ell-1}}$ .

To complete the analysis, notice that each of the two messages that are sent by a temporary leader in phase  $\ell$ , is forwarded at most to distance  $2^{\ell}$ , and then returns the same distance. Thus, each processor that starts phase  $\ell$  is responsible for at most  $4 \cdot 2^{\ell}$  messages. By Lemma 2.3.1, the number of processors that start phase  $\ell$  is at most  $\frac{n}{2^{\ell-1}}$ . Thus, the total number of messages sent in each phase is at most 8n. Since there are n processors, there are at most  $\lceil \log n \rceil$  phases and therefore, the total number of messages that are sent in the algorithm is at most  $8n \log n$ .<sup>1</sup>

To conclude, we have shown a leader election algorithm whose message complexity is  $O(n \log n)$ . Notice that, in contrast to the simple algorithm of the previous section, we use the fact that the ring is bidirectional.

### **2.3.3** An $\Omega(n \log n)$ Lower Bound

In this section, we show that the leader election algorithm of the previous section is optimal. That is, we show that any algorithm for electing a leader in an asynchronous ring sends at least  $\Omega(n \log n)$  messages. The lower bound we prove is for uniform rings where the size of the ring is unknown. The same lower bound holds for non-uniform rings as well, but the proof is much more involved, and is not presented here; see the bibliographic notes at the end of this chapter.

We prove the lower bound for a special variant of the leader election problem, where the elected leader must be the processor with the maximal id in the ring; in addition, all the processors must know who is the elected leader. That is, before terminating each processor writes to a special variable the identity of the elected leader. The proof of the lower bound for the more general definition of the leader election problem follows by reduction and is left as an exercise to the reader.

Assume we are given a uniform algorithm A that solves the above variant of the leader election problem. We will show that there exists an execution of A in which  $\Omega(n \log n)$ messages are sent. Intuitively, this is done by building a wasteful execution of the algorithm for rings of size n/2, in which many messages are sent. Then, we "paste" together two different rings of size n/2 to form a ring of size n, in such a way that we can combine the wasteful executions of the smaller rings and force  $\Theta(n)$  additional messages to be sent.

$<sup>^{1}</sup>$ This is not the optimal bound, in terms of constant factors; see the bibliographic notes at the end of this chapter.

Before presenting the details of the lower bound proof, we first define executions that can be "pasted" together.

**Definition 2.3.1** An execution  $\alpha$  is open if there exists an edge e such that in  $\alpha$  no message is delivered over the edge e; e is the disconnected edge of  $\alpha$ .

Intuitively, since the processors do not know the size of the ring, we can paste two open executions of two small rings to form an open execution of a larger ring. Note that this argument relies on the fact that the algorithm is uniform and works in the same manner for every ring size. We start with the following lemma that considers rings of size 2, and provides the induction base for the recursive pasting process.

**Lemma 2.3.2** For every ring R of size 2, there exists an open execution of A in which at least one message is sent.

**Proof:** Assume R contains processors  $p_1$  and  $p_2$ . Let  $\alpha$  be an infinite execution of A on the ring, and let  $\alpha'$  be the shortest prefix of  $\alpha$  in which both processors are in their final states.

Assume, without loss of generality, that  $p_1$  is chosen as the leader in  $\alpha'$ ; thus,  $p_2$  must terminate by writing "The leader is  $p_1$ ". Note that at least one message must be sent in  $\alpha'$ ; otherwise, if  $p_2$  does not get a message from  $p_1$  it does not know the id of  $p_1$ , and can not write out "The leader is  $p_1$ ". Let  $\alpha''$  be the shortest prefix of  $\alpha'$  that includes the first event of sending a message. Since no message arrives at its destination in  $\alpha''$ , and since one message is sent in  $\alpha''$ , it is clearly an open execution that satisfies the requirements of the lemma.

For clarity of presentation, we assume that n is an integral power of 2 for the rest of the proof. Standard padding techniques can be used to prove the lower bound for other values of n.

As mentioned before, the general approach is to take two open executions (on smaller rings) in which many messages are sent, and to paste them together into an open execution (on the bigger ring) in which the same messages plus extra messages are sent. Intuitively, one can see that two open executions can be pasted together and still behave the same (this will be proved formally below). The key step, however, is forcing the additional messages to be sent. The intuitive idea is that after the two smaller rings are pasted together, at least one half must learn about the leader of the other half. We unblock the messages

delayed on the connecting edges, continue the execution, arguing that many messages must be sent. Our main problem is how to do that in a way that will yield an open execution on the bigger ring (so that the lemma can be applied inductively). The difficulty is that if we pick in advance which of the two edges connecting the two parts to unblock, then the algorithm can choose to wait for information on the other edge. To avoid this problem, we first create a "test" execution, learning on which of the two edges the algorithm will transfer the information between the two connected parts. We then go back to our original pasted execution and only unblock that edge.

Before proceeding with the formal proof we need one additional definition. We say that two rings (i.e., assignments of id's to processors)  $R_1$  and  $R_2$  are *compatible* if the sets of id's in  $R_1$  and  $R_2$  are disjoint. Intuitively, two compatible rings can be combined to produce a legal assignment of id's to a larger ring. The next lemma provides the inductive step of the above pasting process.

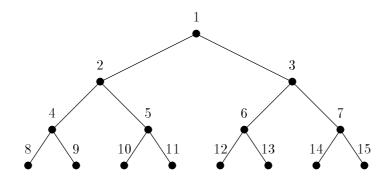

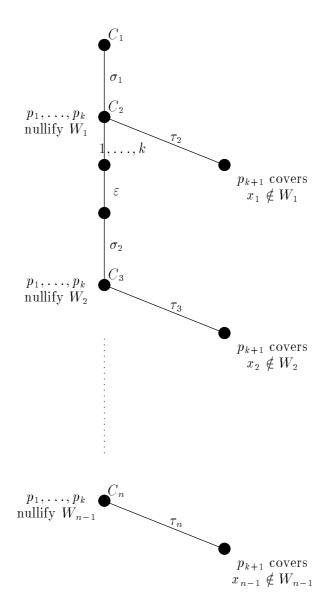

**Lemma 2.3.3** Let  $R_1$  and  $R_2$  be two compatible rings of size k. Assume that there is an open execution of A on  $R_1$  in which at least M(k) messages are sent and similarly for  $R_2$ . Then there is a ring R of size 2k with id's from the set  $R_1 \cup R_2$ , such that there exists an open execution of A on R in which at least  $2M(k) + \frac{k-1}{2}$  messages are sent.

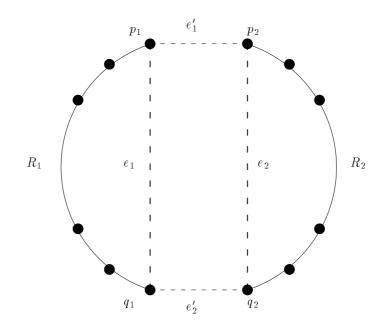

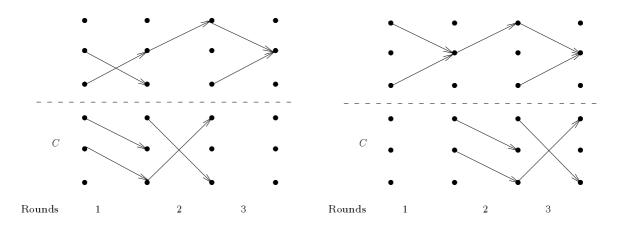

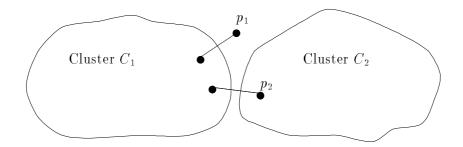

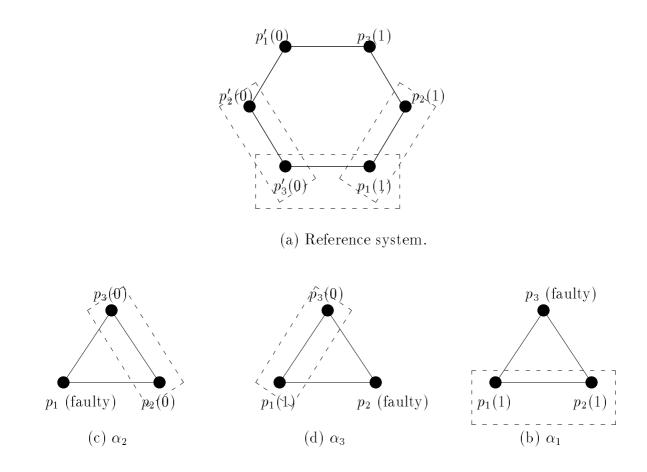

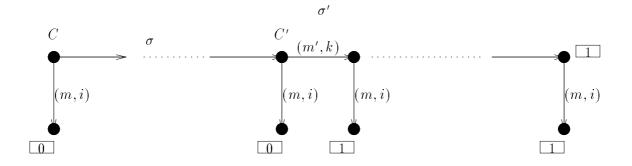

**Proof:** Let  $\alpha_1$  and  $\alpha_2$  be open executions of A on  $R_1$  and  $R_2$ , respectively, in which M(k) messages are sent. Let  $e_1$  and  $e_2$  be the disconnected edges of  $\alpha_1$  and  $\alpha_2$ , respectively. Denote the processors adjacent to  $e_1$  by  $p_1$  and  $q_1$ , and the processors adjacent to  $e_2$  by  $p_2$  and  $q_2$ . Paste  $R_1$  and  $R_2$  together by connecting  $p_1$  to  $p_2$  with edge  $e'_1$  and  $q_1$  to  $q_2$  with edge  $e'_2$ ; denote the ring we obtain by R. (This is illustrated in Figure 2.2.)

We now show how to construct an open execution  $\alpha$  of A on R in which  $2M(k) + \frac{k-1}{2}$  messages are sent.

Consider first the execution  $\alpha_1\alpha_2$ . That is, we let each of the smaller rings execute its wasteful open execution separately. We first apply the events of  $\alpha_1$  to R. Since the processors in  $R_1$  can not distinguish in  $\alpha_1$  whether  $R_1$  is an independent ring or a sub-ring of R, they execute the events of  $\alpha_1$  exactly as if  $R_1$  was independent. We then apply the events of  $\alpha_2$  to R. Again, since no messages are delivered on the edges that connect  $R_1$  and  $R_2$ , processors in  $R_2$  again can not distinguish in  $\alpha_2$  whether  $R_2$  is an independent ring or a sub-ring of R. Thus,  $\alpha_1\alpha_2$  is an execution on R in which at least 2M(k) messages are sent. We now show how to force the algorithm into sending  $\frac{k-1}{2}$  additional messages by unblocking either  $e'_1$  or  $e'_2$ .

Figure 2.2: Pasting  $R_1$  and  $R_2$  into R.

Before proceeding to unblock  $e'_1$  and  $e'_2$  we first bring the ring into a *quiescent* configuration, that is, a state in which there are no messages in transit, except on the disconnected edges.

**Claim 2.3.4** There exists a finite execution  $\alpha_1\alpha_2\alpha_3$  such that  $C_{end}(\alpha_1\alpha_2\alpha_3)$  is quiescent and not all processors have terminated in  $\alpha_1\alpha_2\alpha_3$ .

**Proof:** Let  $\alpha'_3$  be an arbitrary infinite execution extending  $\alpha_1 \alpha_2$  in which no message is delivered on  $e'_1$  or  $e'_2$ . All messages not on  $e'_1$  or  $e'_2$  are delivered immediately.

If  $\alpha_1 \alpha_2 \alpha'_3$  does not contain a quiescent configuration, then the number of messages sent in  $\alpha_1 \alpha_2 \alpha'_3$  is unbounded. Since no messages are delivered on  $e'_1$  or  $e'_2$ , there is a prefix of  $\alpha_1 \alpha_2 \alpha'_3$  which is the desired open execution of the algorithm, completing the proof of the lemma.

Otherwise,  $\alpha_1 \alpha_2 \alpha'_3$  contains a quiescent configuration, so let  $\alpha_1 \alpha_2 \alpha_3$  be the shortest prefix of it that contains a quiescent configuration. We claim that A is not terminated at  $C_{end}(\alpha_1 \alpha_2 \alpha_3)$ . Otherwise, we derive a contradiction in the same way as in the proof of Lemma 2.3.2: Without loss of generality, we assume the elected leader is in  $R_1$ . Since no message is delivered from  $R_1$  to  $R_2$ , processors in  $R_2$  do not know the id of the leader, and therefore can not terminate.

Assume now, without loss of generality, that the processor with the maximal id in R is in the sub-ring  $R_1$ . We claim that in every admissible execution extending  $\alpha_1\alpha_2\alpha_3$ , every processor in the sub-ring  $R_2$  must receive at least one additional message before terminating. This holds since a processor in  $R_2$  can learn the id of the leader only through messages that arrive from  $R_1$ . Since in  $\alpha_1\alpha_2\alpha_3$  no message is delivered between  $R_1$  and  $R_2$ , such a processor will have to receive another message before it can terminate.

The above argument clearly implies that an additional  $\Omega(k)$  messages must be sent on R. However, we cannot conclude our proof here since the above claim assumes that both  $e'_1$  and  $e'_2$  are unblocked (since the execution has to be admissible), and thus the resulting execution is not open. We cannot claim a priori that if we unblock  $e'_1$  many messages will be sent, since the algorithm might decide to wait for messages on  $e'_2$ . However, we can prove that it suffices to unblock only one of  $e'_1$  or  $e'_2$  (we do not know which in advance) and still force the algorithm to send  $\Omega(k)$  messages. This is done in the next claim.

**Claim 2.3.5** There exists a finite execution segment  $\alpha_4$  in which  $\frac{k-1}{2}$  message are sent, such that  $\alpha_1 \alpha_2 \alpha_3 \alpha_4$  is an open execution, in which either  $e'_1$  or  $e'_2$  is disconnected.

**Proof:** Let  $\alpha_4''$  be an arbitrary extension of  $\alpha_1 \alpha_2 \alpha_3$  in which messages are delivered on  $e_1'$  and  $e_2'$  and the algorithm terminates. As we argued before, since each of the processors in  $R_2$  must receive a message before termination, at least k messages are sent in  $\alpha_4''$  before A terminates. Let  $\alpha_4'$  be the shortest prefix of  $\alpha_4''$  in which at least k-1 messages are sent. Consider all the processors in  $R_2$  that received messages in  $\alpha_4'$ . Since we started from a quiescent configuration in which messages were delayed only on  $e_1'$  and  $e_2'$ , these processors form two consecutive sets of processors P and Q; P contains  $p_2$ , while Q contains  $q_2$ . Since at most k-1 processors are included in these sets and the sets are consecutive, it follows that the two sets are disjoint. Furthermore, the number of messages delivered to processors in one of the sets is at least  $\frac{k-1}{2}$ . Without loss of generality, assume this set is P, i.e., the one containing  $p_2$ . Let  $\alpha_4$  be the subsequence of  $\alpha_4'$  that contains only the events on processors in P. Since in  $\alpha_4'$  there is no communication between processors in P and processors in Q,  $\alpha_1\alpha_2\alpha_3\alpha_4$  is an execution. By assumption, at least  $\frac{k-1}{2}$  messages are sent in  $\alpha_4$ . Furthermore, by construction, no message is delivered on  $e_2'$ . Thus  $\alpha_1\alpha_2\alpha_3\alpha_4$  is the desired open execution.

To summarize, we started with two separate executions on  $R_1$  and  $R_2$ , in which 2M(k) messages were sent. We then forced the ring into a quiescent configuration. Finally, we showed that we can force the ring to send  $\frac{k-1}{2}$  additional messages from the quiescent configuration, while keeping either  $e'_1$  or  $e'_2$  disconnected. Thus, we have constructed an open execution in which the number of messages sent is at least  $2M(k) + \frac{k-1}{2}$ .

Lemma 2.3.3 and Lemma 2.3.2 imply that for any ring of size n, there is an execution of A in which the number of messages sent is M(n), where M(n) is a function that satisfies:

$$M(2) \ge 1$$

and  $M(2n) \ge 2M(n) + \frac{n-1}{2}$  (for  $n > 2$ ).

The reader can verify that M(n) is  $\Omega(n \log n)$ .

### 2.4 Synchronous Rings

We now turn to study the problem of electing a leader in a synchronous ring. Again, we present both upper and lower bounds. For the upper bound, two leader election algorithms that require O(n) messages are presented. Obviously, the message complexity of these algorithms is optimal. However, they are not time bounded, and they use processors' id's in an unusual way. For the lower bound, we show that any algorithm that is restricted to use only comparisons of id's, or is restricted to be time bounded, requires at least  $\Omega(n \log n)$  messages.

### **2.4.1** An O(n) Upper Bound

The proof of the  $\Omega(n \log n)$  lower bound for leader election in an asynchronous ring, presented in the previous section, heavily relied on delaying messages for arbitrarily long period. It is natural to wonder whether better results can be achieved in the synchronous model, where message delay is fixed. As we shall see, in the synchronous model, information can be obtained not only by receiving a message but also by *not* receiving a message in a certain round.

In this section, two algorithms for electing a leader in a synchronous ring are presented. Both algorithms require O(n) messages. The algorithms are presented for a unidirectional ring, where communication is in clockwise direction. Of course, the same algorithms can be used for bidirectional rings. Both algorithms assume that id's are non-negative integers. The first algorithm is non-uniform, and requires all processors in the ring to start (wake-up) at the same round. The second algorithm is uniform, and processors may start in different rounds.

#### The Non-Uniform Algorithm

The non-uniform algorithm elects the processor with the minimal id to be the leader. It works in phases, each consisting of n rounds. In phase i, if there is a processor with id i, it is elected as the leader, and the algorithm terminates. Therefore, the processor with the minimal id is elected.

In more detail, the *i*th phase includes rounds n(i-1) + 1, n(i-1) + 2, ..., n(i-1) + n. At the beginning of the *i*th phase, if a processor's id is *i*, and it has not terminated yet, the processor sends a message around the ring and terminates as a leader. If the processor's id is not *i* and it receives a message in phase *i*, it forwards the message and terminates the algorithm as a non-leader.

Since id's are distinct, it is clear that the unique processor with the minimal id terminates as a leader. Moreover, exactly n messages are sent in the algorithm; these messages are sent in the phase the winner is found. The number of rounds, however, depends on the minimal id in the ring. More precisely, if i is the minimal id, the algorithm takes  $n \cdot i$  rounds.

Note that the algorithm depends on the requirements mentioned—knowledge of n and synchronized start. The next algorithm overcomes these restrictions.

#### The Uniform Algorithm

In the uniform algorithm the size of the ring is not known, and furthermore, the processors do not necessarily start the algorithm simultaneously. More precisely, a processor either wakes up spontaneously in an arbitrary round, or wakes up upon receiving a message from another processor.

The uniform algorithm uses two new ideas. First, messages that originate at different processors are forwarded at different rates. More precisely, a message that originates at processor with id i, is delayed  $2^{i-1}$  rounds at each processor it arrives to, before it is forwarded clockwise to the next processor. Second, to overcome the unsynchronized starts, a preliminary wake-up phase is added. In this phase, processors that wake up send a message around the ring; this message is forwarded without delay. A processor that receives a wake-up message before starting the algorithm does not participate in the algorithm, and will only act as a *relay*, forwarding or swallowing messages. After the preliminary phase the leader is elected among the set of participating processors.

**The algorithm:** Each processor that wakes up spontaneously sends a "wake-up" message containing its id. This message travels at a regular rate (one edge per round) and eliminates all the processors that are not awake when receiving the message. When a wake-up message from processor *i* reaches an awake processor, the message starts to travel at rate  $2^i$  (each processor that receives such a message delays it for  $2^{i-1}$  rounds before forwarding it). A message is in the *first phase* as long as it is forwarded at regular rate, and is in the *second phase* when it is forwarded at a rate of  $2^i$ .

Throughout the algorithm, processors forward messages. However, as in previous leader election algorithms we have seen, processors sometimes swallow messages without forwarding them. In this algorithm, messages are swallowed according to the following rules:

- 1. A participating processor swallows a message if the id in the message is larger than the minimal id it had seen so far (including its own id).

- 2. A relay processor swallows a message if the id in the message is not the minimal id it had seen so far (not including its own id).

As we prove below, n rounds after the first processor wakes up, only second phase messages are left, and the leader is elected among the participating processors. The swallowing rules guarantee that only the participating processor with the smallest id receives its message back, and terminates as a leader. This is proved in the next lemma. **Lemma 2.4.1** Only the processor with the smallest id among the participating processors receives its own message back.

**Proof:** Let  $p_i$  be the participating processor with the smallest id, *i*, and denote its message by  $msg_i$ . (Note that at least one processor must participate in the algorithm.) Clearly, no processor (participating or not) can swallow  $msg_i$ . Furthermore, since  $msg_i$  is delayed a finite time at each processor (at most  $2^i$  rounds),  $p_i$  will eventually receive its message back.

Assume, by way of contradiction, that some other processor  $p_j$ ,  $j \neq i$ , also receives back its message  $msg_j$ . Thus,  $msg_j$  must have passed through all the processors in the ring, including  $p_i$ . But i < j, and since  $p_i$  is a participating processor, it will not forward  $msg_j$ . A contradiction.

The above lemma implies that exactly one processor receives its message back. Thus this processor will be the only one to declare itself a leader, implying the correctness of the algorithm. We now analyze the number of messages sent during an execution of the algorithm.

Note that since i is the minimal id, no processor forwards a message after it forwards  $msg_i$ . Once  $msg_i$  returns to  $p_i$ , all the processors in the ring had already forwarded it. Thus we have:

#### **Lemma 2.4.2** No message is forwarded after $msg_i$ returns to $p_i$ .

In order to calculate the number of messages sent during an execution of the algorithm we divide them into three categories: (a) first phase messages, (b) second phase messages sent before the message of the eventual leader enters its second phase, and (c) second phase messages sent after the message of the eventual leader enters its second phase.

**Lemma 2.4.3** The total number of messages in the first category is at most n.

**Proof:** We show that at most one first phase message is forwarded by each processor, which implies the lemma.

Assume, by way of contradiction, that  $p_k$  forwarded two messages in their first phase,  $msg_i$  and  $msg_j$ . Assume, without loss of generality, that  $p_i$  is closer to  $p_k$  then  $p_j$ . Thus,  $msg_j$  must pass  $p_i$  before it arrives to  $p_k$ . If  $msg_j$  arrives to  $p_i$  after it woke up and sent  $msg_i$ ,  $msg_j$  continues as a second phase message (at a rate of  $2^j$ ); otherwise,  $p_i$  will not participate and  $msg_i$  will not be sent. Thus, either  $msg_j$  arrives to  $p_k$  as a second phase message, or  $msg_i$  is not sent. A contradiction.

Let r be the first round in which some processor started executing the algorithm, and let  $p_i$  be one of these processors. To bound the number of messages in the second category, we first show that n rounds after the first processor starts executing the algorithm, all messages are in their second phase.

**Lemma 2.4.4** If  $p_j$  is at (clockwise) distance k from  $p_i$ , then a first phase message is received by  $p_j$  no later than round r + k,

**Proof:** The proof is by induction on k. The base case, k = 1, is obvious since  $p_i$ 's neighbor receives  $p_i$ 's message in round r+1. For the induction step, assume that at round (r+k-1) the processor at (clockwise) distance k-1 from  $p_i$  receives a first phase message. If this processor was already awake, it had already sent a first phase message to its neighbor  $p_j$ , otherwise it will forward the first phase message to  $p_i$  in round (r+k).

Lemma 2.4.5 The total number of messages in the second category is at most n.

**Proof:** By the proof of Lemma 2.4.3, at most one first phase message is sent on each edge. Since by round (r + n) one first phase message was sent on every edge, it follows that after round (r + n) no first phase messages are sent. By Lemma 2.4.4, the message of the eventual leader enters its second phase at most n rounds after the first message of the algorithm is sent. Thus, messages from the second category are sent only in the n rounds following the round in which the first processor woke up.

A message in its second phase with id *i* is delayed  $2^i$  rounds before being forwarded. Thus, a message with id *i* is sent at most  $\frac{n}{2^i}$  times in this category. Since processors with smaller id's send more messages, the maximal number of messages is obtained when all the processors participate, and when the id's are as small as possible, that is,  $0, 1, \ldots, (n-1)$ . Also, second phase message of the eventual leader (in our case, 0) are not counted. Thus, an upper bound on the number of messages in this category is at most  $\sum_{i=1}^{n-1} \frac{n}{2^i} \leq n$ .

**Lemma 2.4.6** The total number of messages in the third category is at most 2n.

**Proof:** Let  $p_i$  be the eventual leader with id i, and let  $p_j$  be some other participating processor with id j. By Lemma 2.4.1, i < j. By Lemma 2.4.2, there are no messages in the ring after  $p_i$  receives its message back. Since  $msg_i$  is delayed  $2^i$  rounds at each processor,  $n2^i$  rounds are needed for  $msg_i$  to return to  $p_i$ . Therefore, messages in the third category are sent only during  $n2^i$  rounds. During these rounds,  $msg_j$  is forwarded at most  $\frac{1}{2^j}n2^i = n2^{i-j}$  times. Hence, the total number of messages transmitted in this category is at most  $\sum_{j \in n} \frac{n}{2^{j-i}}$ . By the same argument as in the proof of Lemma 2.4.5, this is less than or equal to  $\sum_{j=0}^{n-1} \frac{n}{2^j} \leq 2n$ .

Lemmas 2.4.3, 2.4.5, and 2.4.6 imply:

**Theorem 2.4.7** There is a synchronous leader election algorithm whose message complexity is 4n.

By Lemma 2.4.2, the computation ends when the elected leader receives its message back. This happens within  $O(n2^i)$  rounds, where *i* is the id of the elected leader.

### **2.4.2** An $\Omega(n \log n)$ Lower Bound for Restricted Algorithms

In the previous section, we presented two algorithms for electing a leader in synchronous rings whose worst-case message complexity is O(n). Both algorithms have two undesired properties. First, they use the id's in a non-standard manner (to decide how long should a message be delayed). Second, the number of rounds in each execution depends on the id's of processors.

In this section, we show that both these properties are inherent for any message-efficient algorithm. Specifically, we show that if an algorithm uses the id's only for comparisons it requires  $\Omega(n \log n)$  messages. Then we show, by reduction, that if an algorithm is restricted to use a bounded number of rounds, then it also requires  $\Omega(n \log n)$  messages.

#### **Comparison Based Algorithms**

In this section, we formally define the concept of comparison-based algorithms that only compare processors' id's.

For the purpose of the lower bound, we assume that all processors begin their execution at the same round.

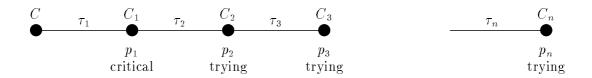

Note that in the synchronous model an execution of the algorithm is completely defined by the initial configuration (there is no choice of message delay). The initial configuration of the system, in turn, is completely defined by the *id assignment*, that is, the sequence of id's obtained by listing the id's clockwise, starting with the minimal id. Two processors,  $p_1$ in ring  $R_1$  and  $p_2$  in ring  $R_2$ , are *matching* if they have the same position in the respective id assignments. Note that matching processors are at the same distance from the processor with the smallest id in the respective id assignments.

Intuitively, an algorithm is comparison based if it behaves the same on rings that have the same order pattern. Formally, two id assignments,  $x_1, \ldots, x_n$  and  $y_1, \ldots, y_n$ , are order equivalent if for every  $i, j, x_i < x_j$  if and only if  $y_i < y_j$ ; two rings,  $R_1$  and  $R_2$ , are order equivalent

if their id assignments are order equivalent. Recall that the *k*-neighborhood of a processor  $p_i$  in a ring is the sequence of 2k+1 id's of processors  $p_{i-k}, \ldots, p_{i-1}, p_i, p_{i+1}, \ldots, p_{i+k}$  (all indices are calculated modulo n). We extend the notion of order equivalence to *k*-neighborhoods in the obvious manner.

We now define what it means to "behave the same". Intuitively, we would like to claim that in the executions on order-equivalent rings  $R_1$  and  $R_2$ , the same messages are sent and the same decisions are made. In general, however, messages sent by the algorithm contain id's of processors; thus, messages sent on  $R_1$  will be different from messages sent on  $R_2$ . For our purpose, however, we concentrate on the message pattern, that is, when and where messages are sent, rather than their content, and on the decisions. Specifically, consider two executions  $\alpha_1$  and  $\alpha_2$  and two processors  $p_i$  and  $p_j$ . We say that the behaviors of  $p_i$  in  $\alpha_1$  is similar in round k to the behavior of  $p_j$  in  $\alpha_2$  if the following conditions are satisfied:

- 1.  $p_i$  sends a message to its left (right) neighbor in round k in  $\alpha_1$  if and only if  $p_j$  sends a message to its left (right) neighbor in round k in  $\alpha_2$ , and

- 2.  $p_i$  decides it is a leader in round k of  $\alpha_1$  if and only if  $p_j$  decides it is a leader in round k of  $\alpha_2$ .

We say that that the behaviors of  $p_i$  in  $\alpha_1$  and  $p_j$  in  $\alpha_2$  are *similar* if they are similar in all rounds  $k \ge 0$ . We can now formally define comparison based algorithms.

**Definition 2.4.1** An algorithm A is comparison based if for any pair of order equivalent rings  $R_1$  and  $R_2$ , any pair of matching processors have similar behaviors in the respective executions of A on  $R_1$  and  $R_2$ .

#### Lower Bound for Comparison Based Algorithms

Let A be a comparison based leader election algorithm. The proof goes by considering an id assignment that is highly symmetric in its order patterns, that is, an id assignment in which there are many order equivalent neighborhoods. Intuitively, as long as two processors have order equivalent neighborhoods they behave the same under A. We derive the lower bound by executing A on a highly symmetric ring, and arguing that if a processor sends a message in a certain round, then all processors with order equivalent neighborhoods also send a message in that round.

A crucial point in the proof is to distinguish rounds in which information is obtained by processors from rounds in which no information is obtained. Recall that in a synchronous ring it is possible for a processor to obtain information even without receiving a message. For example, in the non-uniform algorithm, the fact that no message is received in rounds  $1, \ldots, n$  implies that no processor in the ring has the id 1. The key to the proof that follows is the observation that the nonexistence of a message in a certain round r is useful to processor  $p_i$  only if a message could have been received in this round (in a different id assignment). For example, in the non-uniform algorithm, if some processor in the ring had the id 1, a message would have been received in rounds  $1, \ldots, n$ . Thus, a round in which no message is sent on any order-equivalent ring is not useful. Such useful rounds are called active, as defined below:

**Definition 2.4.2** A round r is active in the execution on a ring R if some processor sends a message in round r. We denote by  $r_k$  the index of the kth active round.<sup>2</sup>

Recall that, by definition, a comparison based algorithm generates similar behaviors on order equivalent rings. This implies that, for order equivalent rings  $R_1$  and  $R_2$ , a round is active on  $R_1$  if and only if it is active on  $R_2$ .

It is fairly obvious that the state of a processor after round k depends only on its k-neighborhood. We have, however, a stronger property that the state of a processor after the kth active round depends only on its k-neighborhood. This captures the above intuition that information is obtained only in active rounds, and is formally proved in the next lemma. Note that the lemma does not require that the processors are matchings (otherwise the claim follows immediately from the definition), but does require that their neighborhoods are identical.

**Lemma 2.4.8** Let  $R_1$  and  $R_2$  be order equivalent rings, and let  $p_1$  in  $R_1$  and  $p_2$  in  $R_2$  be two processors with identical k-neighborhoods. Then  $p_1$  and  $p_2$  are in the same state after rounds  $1, \ldots, r_k$ .

**Proof:** Informally, the proof shows that after k active rounds, a processor may learn only about processors that are at most k away from itself.

The formal proof follows by induction on k. For the base case k = 0, note that two processors with identical 0-neighborhood have the same id's, and thus they are in the same state.

For the induction step, assume that any two processors with identical (k - 1)neighborhood are in the same state after the (k - 1)th active round. Since  $p_1$  and  $p_2$

$<sup>^{2}</sup>$ Recall that once the initial id assignment is fixed, the whole execution is determined since the system is synchronous.

have identical k-neighborhoods, they also have identical (k - 1)-neighborhoods; therefore, by the induction hypothesis,  $p_1$  and  $p_2$  are in the same state after the (k - 1)th active round. Furthermore, their respective neighbors have identical (k - 1)-neighborhoods. Therefore, by the induction hypothesis, their respective neighbors are in the same state after the (k - 1)th active round.

In the rounds between the (k-1)th active round and the kth active round (if there are any) no processor receives any message and thus  $p_1$  and  $p_2$  remain in the same state as each other, and so do their respective neighbors. (Note that  $p_1$  might change its state during the non-active rounds, but since  $p_2$  has the same transition function, it makes the same state transition.) In the kth active round, if both  $p_1$  and  $p_2$  do not receive messages they are in the same states at the end of the round. If  $p_1$  receives a message from its right neighbor,  $p_2$  also receives an identical message from its right neighbor, since the neighbors are in the same state, and similarly for the left neighbor. Hence,  $p_1$  and  $p_2$  are in the same state at the end of the kth active round, as needed.

The next lemma carries the above claim from processors with identical k-neighborhoods to processors with order equivalent k-neighborhoods. It relies on the fact the A is comparison based. Furthermore, it requires that the id's in R's id assignment are spaced, which intuitively means that for any two id's in R there are n id's between them. Formally, a set of id's X is *spaced* if for every id  $x \in X$ , it holds that  $x \pm i \notin X$ , for i = 1, ..., n. Note that the next lemma does not require that the two processors are matching processors in order equivalent rings.

**Lemma 2.4.9** Let R be a ring with a spaced id assignment, and let  $p_1$  and  $p_2$  in R be two processors with order equivalent k-neighborhoods. Then  $p_1$  and  $p_2$  have similar behaviors in rounds  $1, \ldots, r_k$ .

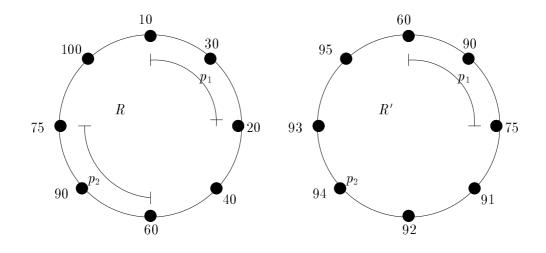

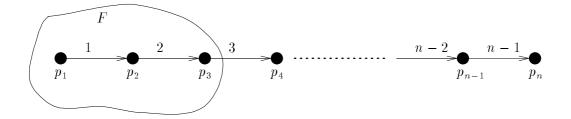

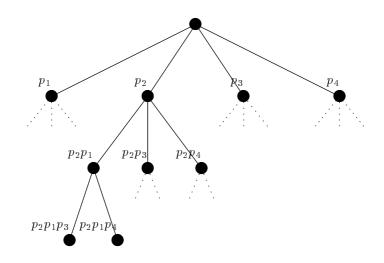

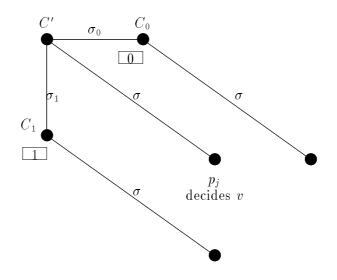

**Sketch of proof:** Let  $\vec{x}$  be  $p_1$ 's k-neighborhood and let  $\vec{y}$  be  $p_2$ 's k-neighborhood; by assumption,  $\vec{x}$  and  $\vec{y}$  are order equivalent. We embed the  $\vec{x}$  in an id assignment for a ring R' which is order equivalent to R, such that  $\vec{x}$  corresponds to  $\vec{y}$ . This implies that  $p_1$  in R' is matching to  $p_2$  in R. R' is created by considering the permutation that sorts the id assignment of R (with  $\vec{y}$  as prefix), and using it to extend  $\vec{x}$ . Since the id assignment of R is spaced, we can always find values to match. Furthermore, we can do it while avoiding the id's in  $\vec{x}$ . It follows that the id's in R' are unique and that R' is order equivalent to R. (See an example in Figure 2.3.)

By Lemma 2.4.8, both  $p_1$  in R' and  $p_1$  in R are in the same state after rounds  $1, \ldots, r_k$ . In particular, their behaviors are similar in rounds  $1, \ldots, r_k$ . Since the algorithm is comparison

Figure 2.3: Example for the proof of Lemma 2.4.9; k = 1.

based and  $p_1$  in R' is matching to  $p_2$  in R, they have similar behaviors in rounds  $1, \ldots, r_k$ . Thus,  $p_1$  and  $p_2$  in R have similar behaviors in rounds  $1, \ldots, r_k$ .

Given this lemma, we proceed to show that a comparison based algorithm sends many messages on highly symmetric rings. We first precisely define highly symmetric rings.

**Definition 2.4.3** Let a and b be two nonnegative real numbers. A ring is (a, b)-fooling if for every k < an, and for every k-neighborhood on the ring, there are at least  $\lceil \frac{bn}{2k+1} \rceil$  order equivalent k-neighborhoods on the ring.

We proceed by showing how we can force A to send many messages when it is executed on an (a, b)-fooling ring. Later we show that such rings exist.

**Theorem 2.4.10** Let a and b be two nonnegative real numbers, and assume  $\frac{bn}{2an+1} > 1$ . If R is an (a,b)-fooling ring, with a spaced id assignment, then at least  $\frac{bn}{3} \ln an$  messages are sent in the execution of A on R.

**Proof:** Let T be the number of active rounds in the execution of A on R.

Claim 2.4.11  $T \ge an$ .

**Proof:** Assume, by way of contradiction, that T < an. Assume that the leader elected by A is  $p_i$ . Since the ring is (a, b)-fooling, and since T < an, there are at least  $\lceil \frac{bn}{2T+1} \rceil$  order equivalent T-neighborhoods on the ring. Since  $\frac{bn}{2an+1} > 1$ , there exists another processor  $p_j$ , such that the T-neighborhoods of  $p_i$  and  $p_j$  are order equivalent. By Lemma 2.4.9,  $p_i$  and  $p_j$  have similar decisions until the Tth active round. Thus,  $p_j$  also terminates as a leader. A contradiction.

By definition, in each active round at least one processor sends a message. Let  $p_i$  be a processor which sends a message in the *k*th active round, for some  $k \leq an$ . Since *R* is (a, b)-fooling and  $k \leq an$ , there are at least  $\frac{bn}{2k+1}$  processors whose *k*-neighborhood is order equivalent to  $p_i$ 's. By Lemma 2.4.9, these processors have similar behaviors in the *k*th active round and thus, all send a message in the *k*th active round. Therefore, at least  $\frac{bn}{2k+1}$ messages are sent at the *k*th active round.

Summing over all  $k, 1 \le k < an$ , we get that the total number of messages sent during the execution on R is at least

$$\sum_{k=1}^{an-1} \frac{bn}{2k+1} \ge \frac{bn}{3} \sum_{k=0}^{an} \frac{1}{k} \approx \frac{bn}{3} \ln an .$$

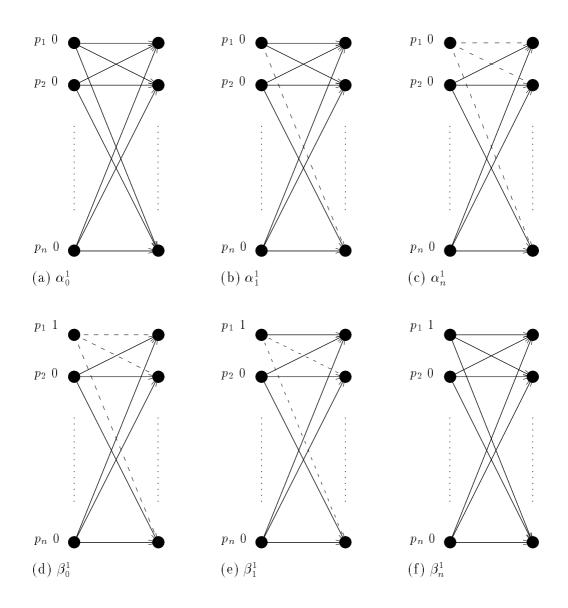

To complete the proof of the lower bound we have to show that there exist (a, b)-fooling rings. The construction of such rings for general n is quite complex and relies on techniques from formal languages theory (see the bibliographic notes). Here we only construct (a, b)-fooling rings of size n, where n is an integral power of 2. In this case,  $a = \frac{1}{4}$  and  $b = \frac{1}{2}$ .

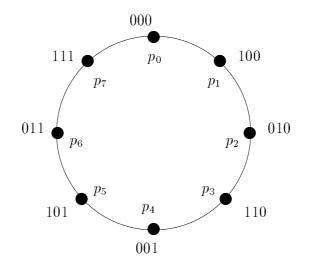

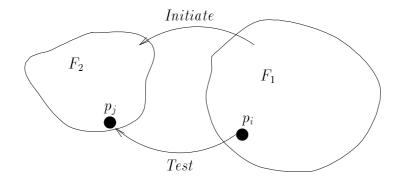

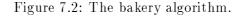

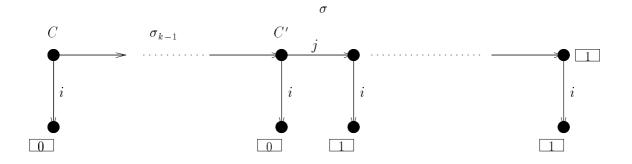

The rings are obtained by assigning to each processor an id which is the reverse of the binary representation of its index (using a reperesentation of fixed length,  $\log n$ ). Specifically, let rev(j) denote the integer whose binary representation (taken as a string of binary digits) is the reverse of the binary representation of j. (See the special case n = 8 in Figure 2.4.)

**Lemma 2.4.12** Let R be a ring whose id assignment is  $rev(0), rev(1), \ldots, rev(n-1)$ . Then R is a  $(\frac{1}{4}, \frac{1}{2})$ -fooling ring.

**Proof:** In R, the *i* most significant bits of processor id's repeatedly cycle through the  $2^i$  possible arrangements. Thus, in every sequence of  $2^i$  consecutive processors, each id differs from any other id (their *i* most significant bits are different).

To prove the lemma we must show that for every  $k < \frac{n}{4}$ , and for every k-neighborhood on the ring, there are at least  $\left\lceil \frac{1}{2} \frac{n}{2k+1} \right\rceil$  order equivalent k-neighborhoods on the ring.

Figure 2.4: Example for n=8.

Let S be an arbitrary sequence of  $2^i$  id's in the ring. Any other sequence of id's of length  $2^i$  starting at a processor which is  $c2^i$  away from the first processor in S, for some positive integer c, is order equivalent to S. Thus, there are  $\frac{n}{2^i}$  such sub-sequences, including S itself, that are order equivalent.

To prove the claim for an arbitrary  $k < \frac{n}{4}$ , we use padding arguments. Specifically, pick *i* such that  $2^i \le k < 2^{i+1}$ .

Since  $k < 2^{i+1}$ ,  $2k + 1 < 2^{i+2}$ . Thus any k-neighborhood is contained in some sequence of  $2^{i+2}$  id's. As shown previously, there are at least  $\frac{n}{2^{i+2}}$  order equivalent neighborhoods of size  $2^{i+2}$ . Obviously, in each such neighborhood there is a sequence of 2k + 1 id's which is order equivalent to the original k-neighborhood. Thus, for every k-neighborhood there are at least

$$\frac{n}{2^{i+2}} \ge \left\lceil \frac{1}{2} \frac{n}{2k+1} \right\rceil$$

order equivalent k-neighborhoods.

Formally, to conclude the lower bound we need to take a fooling ring with a spaced id assignment. This is easily achieved by taking the fooling ring constructed in the previous lemma and "blowing it up". Note that  $(n + 1)rev(0), (n + 1)rev(1), \ldots, (n + 1)rev(n - 1)$  is a  $(\frac{1}{4}, \frac{1}{2})$ -fooling ring, with a spaced id assignment.

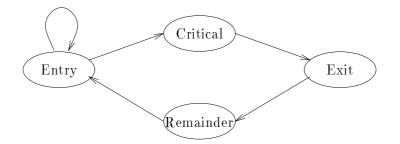

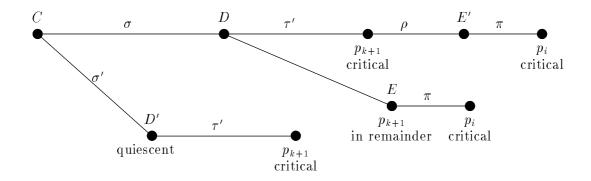

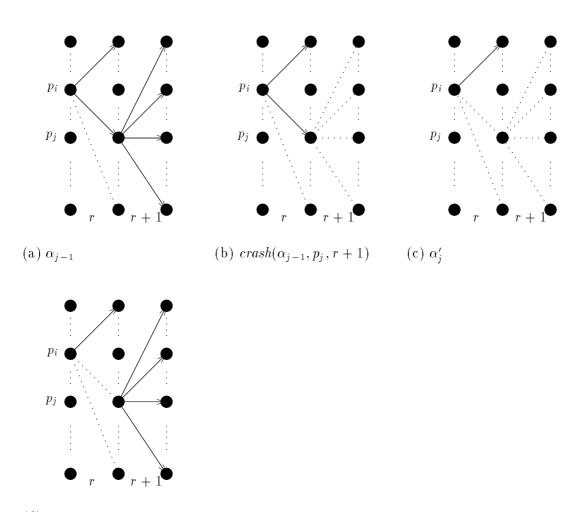

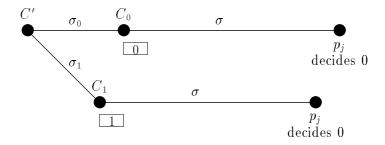

#### Lower Bound for Time-Bounded Algorithms